【創科廣場】IBM推2nm晶片製程 延續摩爾定律神話

2021-05-11 09:28

2nm晶片之所以重要,半導體製程常以納米(nm)製程,計算半導體技術水平;其實是nm是代表了集成電路(Integrated circuit)之中的「閘極長度」(Gate length)是所有,其構造最細小,也最難製作,常常以「閘極長度」代表了半導體製程的水平,也被稱為製程綫寬,又稱「綫寬」。

閘極的綫寬愈小,電晶體愈密集,電晶體密度愈高,則可在更小晶片上,放入更多電晶體;除了提高運算效率和降低功耗,封裝後的集成電路,體積愈小,成本也愈低,電腦或手機體積更輕薄。

一九六五年,英特爾(Intel)創始人Gordon Moore提出了「摩爾定律」(Moore's law):預測集成電路上可容納電晶體數目,約每隔兩年增加一倍,此後一直顛撲不破。但當閘極長度縮小至20nm以下,問題亦接踵而來,包括良率(Yield rate)降低,漏電嚴重。

電晶體密度驚人

2nm晶片較現時主流的7nm製程技術,性能提升了四成半,功耗降低七成半;目前最尖端晶片製程是5nm,而2nm晶片體積更小、速度更快。但最大問題是良率,良率不足,晶片光罩成本極高,成品不斷報廢,代工或IDM面臨嚴重虧損。英特爾就是在受困在10nm和7nm的良率不足,產期一拖再拖。

目前,只有台灣台積電和韓國三星,充分掌握了5nm製程的良率,達到生產級水平,IBM的2nm晶片製程,相信挑戰更大。

據AnandTech網站分析,台積電5nm晶片每平方毫米約容納一億七千三百萬個電晶體,三星5nm每平方毫米只約有一億二千七百萬個電晶體。IBM新型2nm晶片每平方毫米,可約三億三千三百萬個電晶體,代表IBM的2nm內每平方毫米電晶體密度,達到了台積電5nm的兩倍,相當驚人。

閘極長度不一定代表電晶體密度,以英特爾的7nm電晶體密度,電晶體兩億三千七百萬個,超越了台積電5nm,也超過三星7nm。不過,IBM的2nm晶片規格上,仍超越台積電3nm的兩億九千二百萬個電晶體。

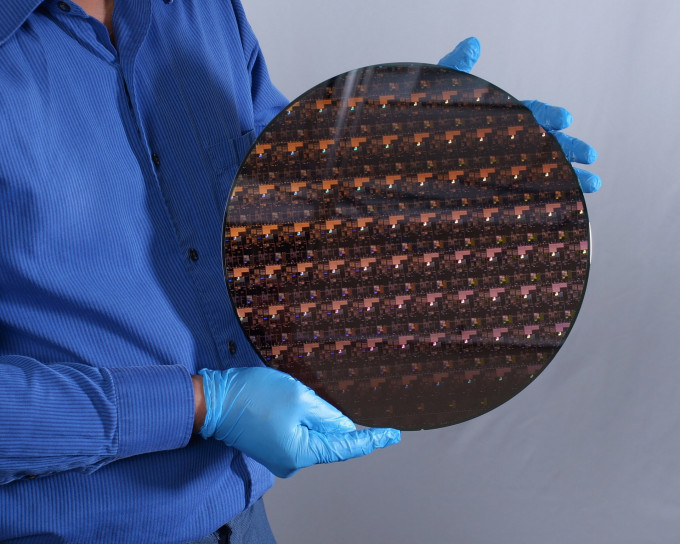

IBM表示,採用2nm工藝製造測試晶片,一塊指甲大小的晶片中,容納了五百億個電晶體,2nm寬度已小於人體DNA的單鏈。

新一代製程GAA

IBM晶片屬於以其三層堆疊納米片GAA(Gate-All-Around)工藝,晶片也首次使用底部電介質隔離,減少漏電,亦有助於減少功耗,晶片另一突破為內部空間乾燥工藝,晶片更廣泛採用EUV光刻技術。

過去數年,FinFET製程成為主流,源於美國加州大學柏克萊研究人員,發明了「鰭式場效電晶體(Fin Field Effect Transistor,FinFET)」,取代原本2D構造的MOSFET工藝,3D結構的FinFET因構造上像魚鰭 ,被稱為「鰭式(Fin)」,半導體閘極長度成功縮小到20nm以下,但到了5nm FinFET又開到荼蘼,由GAA接手解決5nm以後的挑戰。

估計台積電會在2nm工藝製造使用GAA工藝,英特爾則大落後,不知何時開始GAA製程。

藍色巨人屢創先河

IBM在紐約州奧爾巴尼的Albany Nanotech Complex科技綜合園再開發了GAA製程,較早前三星已IBM研究試驗製作3nm晶片,有望取代FinFET工藝。GAA利用特定材料,可將電流通道包裹成3D結構,雖然更複雜,卻可大幅提升電晶體密度,實現2nm和1nm閘極長度,亦解決了漏電問題。

歷史上,IBM科學家在半導體技術有多次突破,一九六○年首先引入倒裝晶片封裝技術,然後是單晶體管DRAM,連精簡指令集(RISC)都是IBM設計,IBM研究人員John Cocke因此獲得了一九八七年圖靈獎,

目前手機ARM處理器就是基於RISC架構,其他SiGe矽工藝、銅互連、絕緣矽、應變矽和Power處理器,無一不對半導體行業,帶來了深遠的影響。如果GAA成功取代FinFET,就再一次證明IBM研究實力,寶刀未老。

關鍵字

最新回應