【创科广场】IBM推2nm晶片制程 延续摩尔定律神话

2021-05-11 09:28

2nm晶片之所以重要,半导体制程常以纳米(nm)制程,计算半导体技术水平;其实是nm是代表了集成电路(Integrated circuit)之中的「闸极长度」(Gate length)是所有,其构造最细小,也最难制作,常常以「闸极长度」代表了半导体制程的水平,也被称为制程綫宽,又称「綫宽」。

闸极的綫宽愈小,电晶体愈密集,电晶体密度愈高,则可在更小晶片上,放入更多电晶体;除了提高运算效率和降低功耗,封装后的集成电路,体积愈小,成本也愈低,电脑或手机体积更轻薄。

一九六五年,英特尔(Intel)创始人Gordon Moore提出了「摩尔定律」(Moore's law):预测集成电路上可容纳电晶体数目,约每隔两年增加一倍,此后一直颠扑不破。但当闸极长度缩小至20nm以下,问题亦接踵而来,包括良率(Yield rate)降低,漏电严重。

电晶体密度惊人

2nm晶片较现时主流的7nm制程技术,性能提升了四成半,功耗降低七成半;目前最尖端晶片制程是5nm,而2nm晶片体积更小、速度更快。但最大问题是良率,良率不足,晶片光罩成本极高,成品不断报废,代工或IDM面临严重亏损。英特尔就是在受困在10nm和7nm的良率不足,产期一拖再拖。

目前,只有台湾台积电和韩国三星,充分掌握了5nm制程的良率,达到生产级水平,IBM的2nm晶片制程,相信挑战更大。

据AnandTech网站分析,台积电5nm晶片每平方毫米约容纳一亿七千三百万个电晶体,三星5nm每平方毫米只约有一亿二千七百万个电晶体。IBM新型2nm晶片每平方毫米,可约三亿三千三百万个电晶体,代表IBM的2nm内每平方毫米电晶体密度,达到了台积电5nm的两倍,相当惊人。

闸极长度不一定代表电晶体密度,以英特尔的7nm电晶体密度,电晶体两亿三千七百万个,超越了台积电5nm,也超过三星7nm。不过,IBM的2nm晶片规格上,仍超越台积电3nm的两亿九千二百万个电晶体。

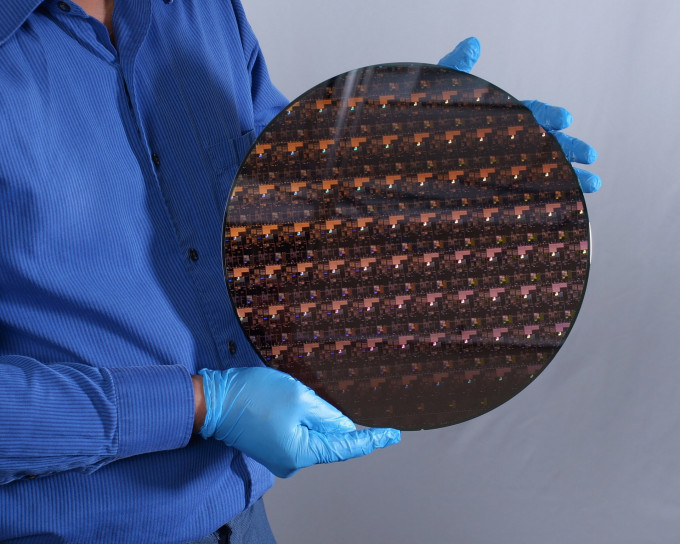

IBM表示,采用2nm工艺制造测试晶片,一块指甲大小的晶片中,容纳了五百亿个电晶体,2nm宽度已小于人体DNA的单链。

新一代制程GAA

IBM晶片属于以其三层堆叠纳米片GAA(Gate-All-Around)工艺,晶片也首次使用底部电介质隔离,减少漏电,亦有助于减少功耗,晶片另一突破为内部空间乾燥工艺,晶片更广泛采用EUV光刻技术。

过去数年,FinFET制程成为主流,源于美国加州大学柏克莱研究人员,发明了「鳍式场效电晶体(Fin Field Effect Transistor,FinFET)」,取代原本2D构造的MOSFET工艺,3D结构的FinFET因构造上像鱼鳍 ,被称为「鳍式(Fin)」,半导体闸极长度成功缩小到20nm以下,但到了5nm FinFET又开到荼蘼,由GAA接手解决5nm以后的挑战。

估计台积电会在2nm工艺制造使用GAA工艺,英特尔则大落后,不知何时开始GAA制程。

蓝色巨人屡创先河

IBM在纽约州奥尔巴尼的Albany Nanotech Complex科技综合园再开发了GAA制程,较早前三星已IBM研究试验制作3nm晶片,有望取代FinFET工艺。GAA利用特定材料,可将电流通道包裹成3D结构,虽然更复杂,却可大幅提升电晶体密度,实现2nm和1nm闸极长度,亦解决了漏电问题。

历史上,IBM科学家在半导体技术有多次突破,一九六○年首先引入倒装晶片封装技术,然后是单晶体管DRAM,连精简指令集(RISC)都是IBM设计,IBM研究人员John Cocke因此获得了一九八七年图灵奖,

目前手机ARM处理器就是基于RISC架构,其他SiGe矽工艺、铜互连、绝缘矽、应变矽和Power处理器,无一不对半导体行业,带来了深远的影响。如果GAA成功取代FinFET,就再一次证明IBM研究实力,宝刀未老。

關鍵字

最新回应